さて、大変遅れたのですが、先日投稿した記事のアンプが完成しましたのでまとめます。

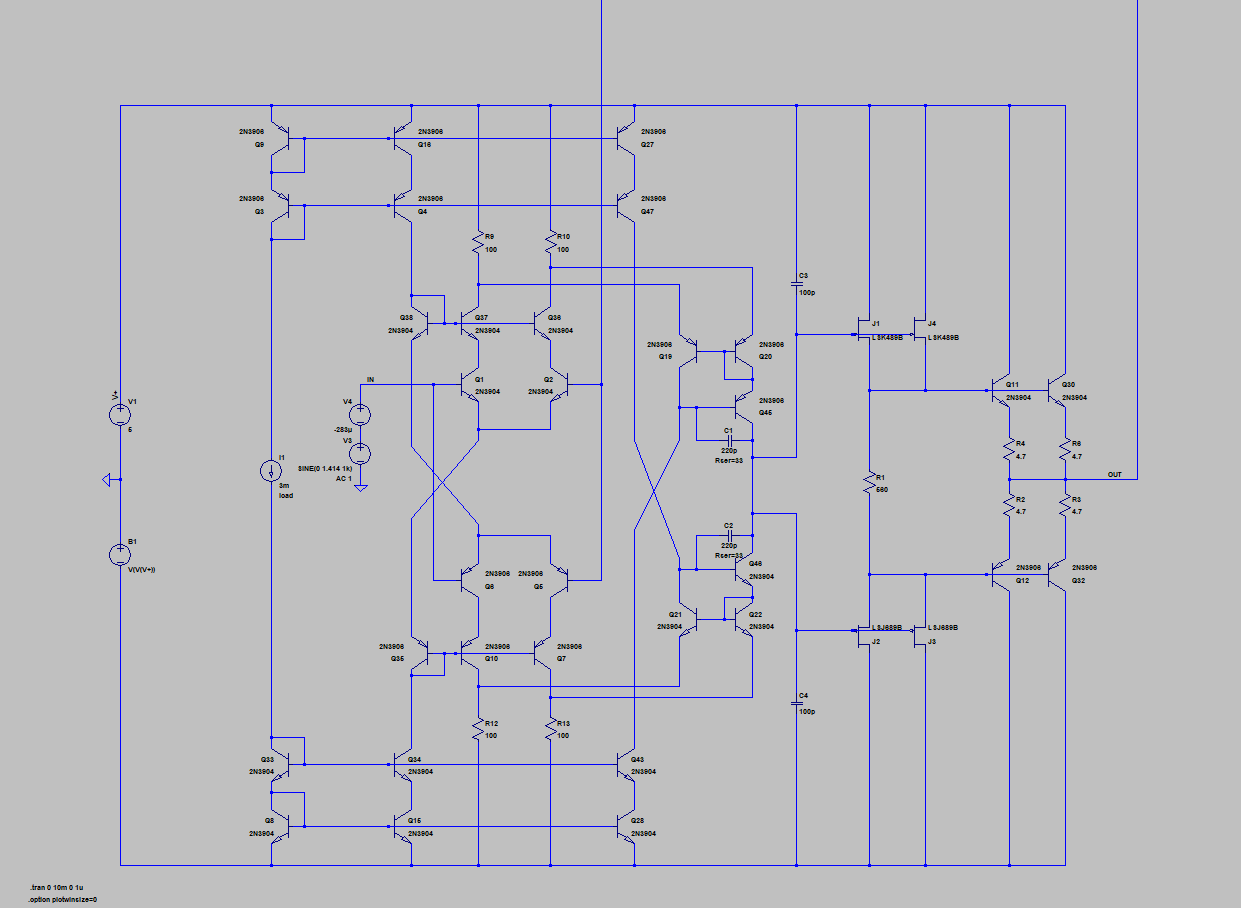

ディスクリートヘッドホンアンプ第二弾

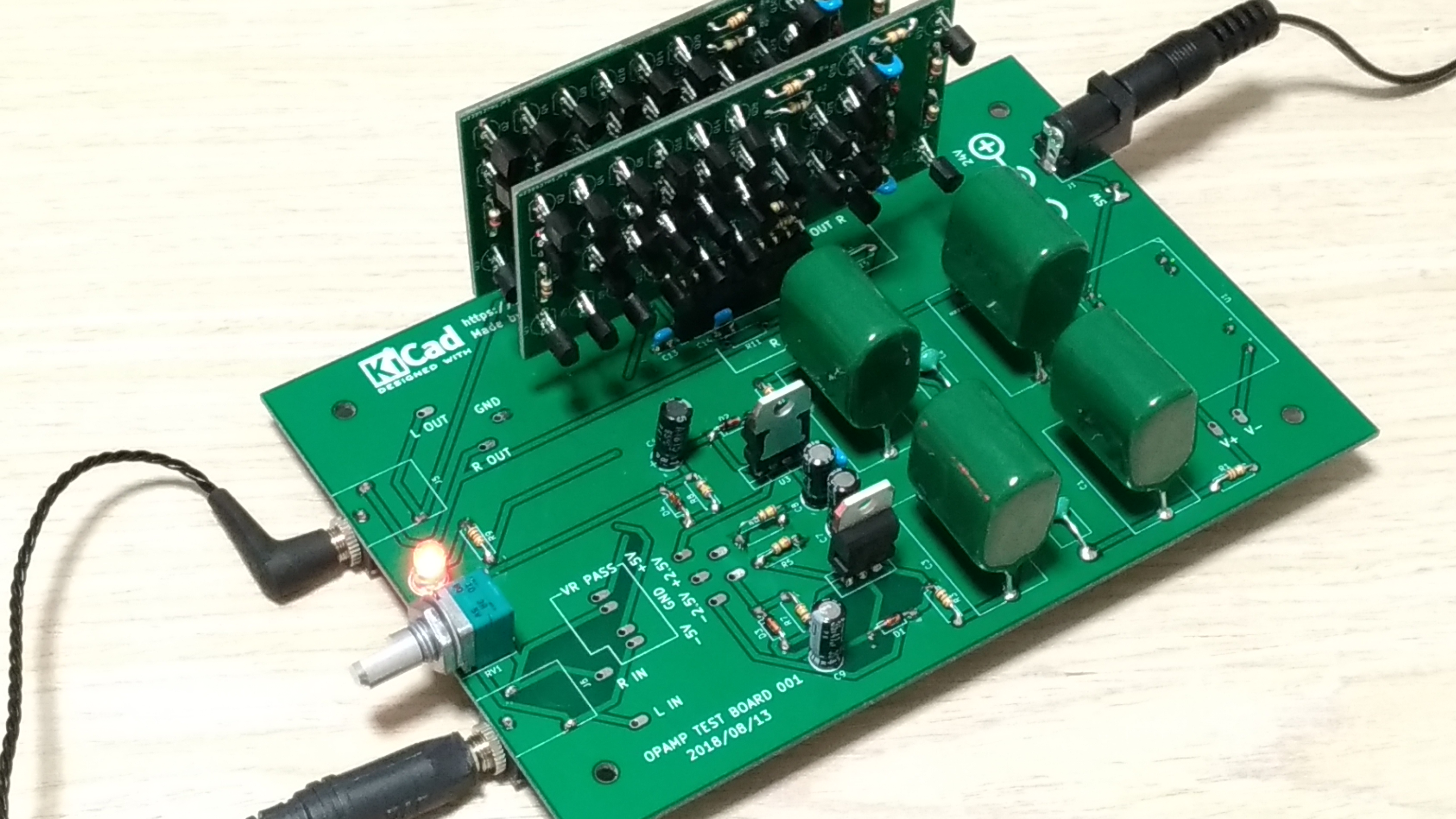

実装図はこちら

意外ときれいにできた気がします。

ただ、ミニジャックとDCDCのフットプリントが上下逆でした…これは反省。

そして、奇跡的に一発で音がでました!

一聴すると、ある意味特徴がない音ですが、非常にノイズが少なくて、歪感も少ないものでした。

そして性能を測定をしてみました。

まずは、無負荷時の最良のTHDから。

高音にたくさん入ってるスペクトルは測定系のものです。THDは0.01%でした。(測定系単体だと0.005%くらい)

まあまあですかね。ちょっと微妙な数値ですが悪くはありません。

次に負荷をかけてみます。

見た感じほぼ変化していません。数値的にも0.01%とそのままです。負荷分離がきちんとできているようです。

という感じですね。まとめますと

負荷の分離はできていて目標は達成

しかし歪みに課題あり

ですね。不完全燃焼だったのでいろいろ改造してみたのですが(電源電圧盛ってみたり、ブートストラップしてみたり、パーツ交換してみたりetc)いまいち良い結果は得られず。

どうも根本的に何かがだめなようで、いろいろ考察してみました。

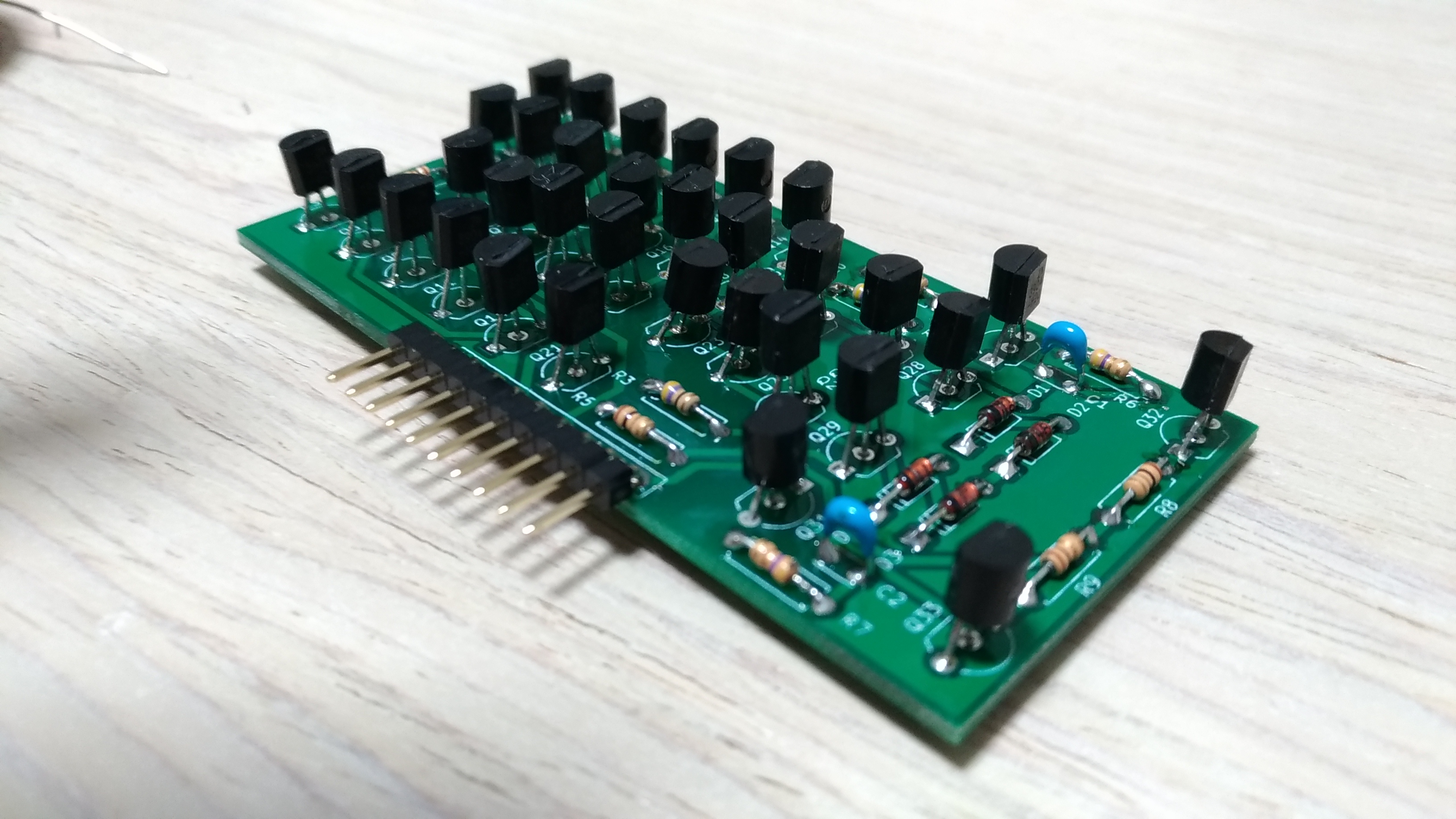

まず今回の回路はこちら。

この回路自体はそんなに悪くないのですが、いくつか問題点がありました。

入力段の非線形な入力容量変化に対する対策がされていない

これはトランジスタのデータシート(2N3904)にも乗っているのですが、

トランジスタのバイアス電圧に対して、容量が変調するというものです。これはシミュレーション上のSPICEには入っていない要素のようで、この原因は排除したいと考えました。

次に、増幅段から出力段までの入力インピーダンスが低すぎて、オープンループゲインが低下している

これはシミュレーション上でもわかることですが、ゲインがあまり高くありません。コレ自体は直接歪の原因にはなりませんが、あったほうが良いものがないのでもったいないわけです。

そして、ここでわかったことがあります。

同時に各トランジスタの動作点が入力に対して変動してしまう

これが直接の原因かと思われます。要は動作点が入力に対して変動してしまうので、そのせいで歪んでると考えました。

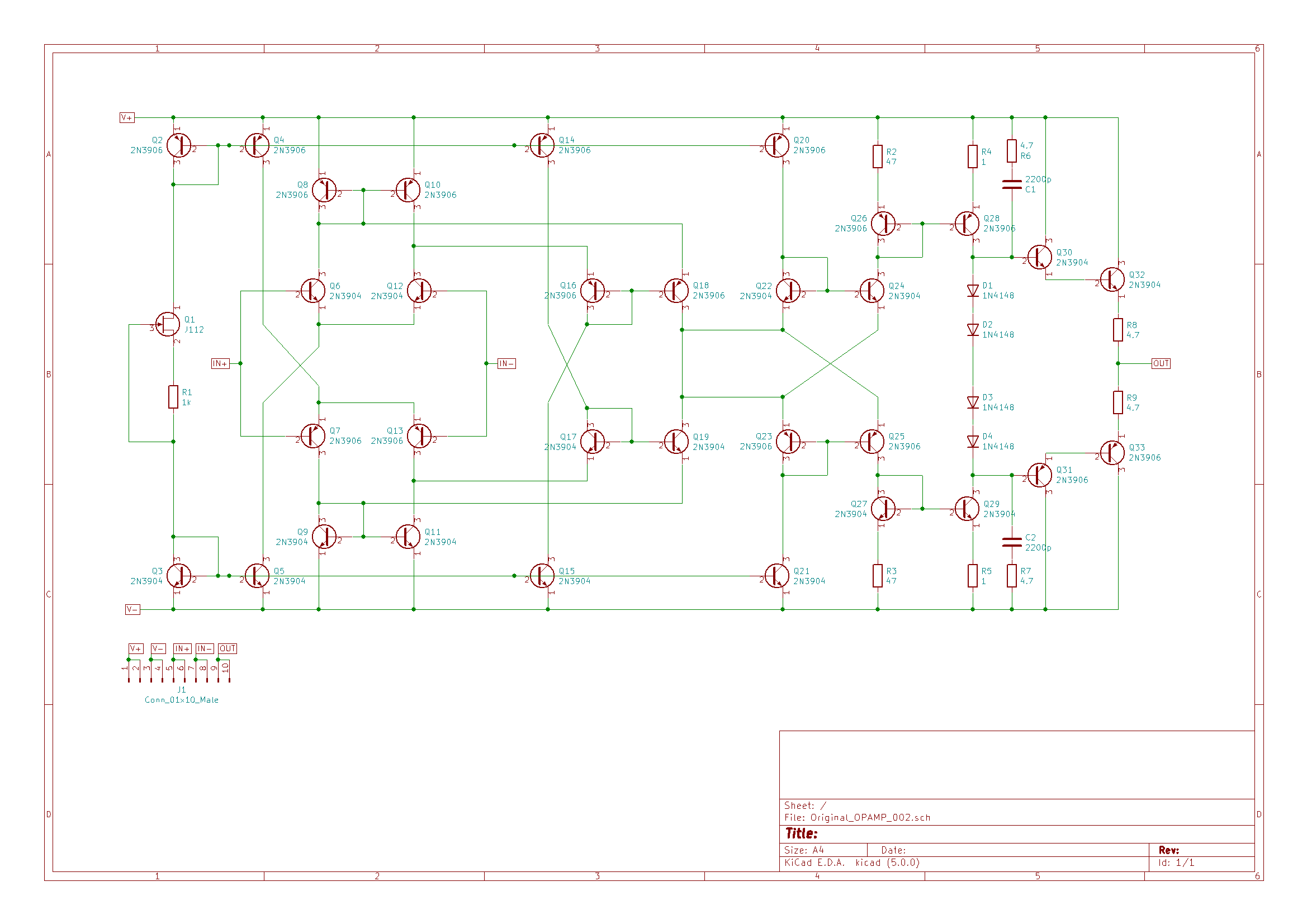

いろいろ考えた結果の回路はこちら。

正直ガラリと変わっています。残っているのは入力部分がコンプリメンタルになっていることくらいです。

定電流源はすべてカスコードしてあり、徹底的に動作点の変動を抑えています。

同時にコンプリメンタルの入力部分もカスコードしてあり、どの入力でも動作点は常に一定となります。これは入力容量の変化に対する対策です。

さらに、フォールデット回路の前のカレントミラーを抵抗としました。(R9 R10 R12 R13)これも歪対策で、線形特性が強いことを利用しています。

フォールデット回路はフィードバック型のカレントミラーとしました。これにより電流の変動を極限まで抑えます。

そして、今まで避けていたのですが、出力段のインプットをJFETとしました。避けていた理由は「使いづらいから」だったのですが、翌々考えてみるとデプレッション特性により簡単にバイアス電圧が取れることが判明。しかも駆動力もそこそこあり、トランジスタみたいにhfeぶんの電流が漏れることもありません。

なので、JFETで上下のバイアスをセットして、そのままエミッタ出力のトランジスタに接続しました。それぞれ2個にしているのは気持ち駆動力を上げたいからで深い意味はありません。

ちなみにシミュレーション上は無歪の出力となります。(THD=-160dB以下)

ここまでやれば大丈夫だろう・・・という感じです。

正直、電源のヘッドルームは完全に犠牲にしていますが。

次回はこれの実装回路を起こしたいと思います。