先週辺りからRail to railのディスクリートオペアンプについて考察し続けています。そして、かなり重要なことがわかりつつあります。今回はそれをまとめようと思います。

Rail to rail オペアンプの良さと悪さ

まず、RtRアンプの良さですが、当然ながら電源レールギリギリまで使えることにあります。ダーリントンにするだけで0.7V×2=1.4Vくらいはヘッドマージンを取らなくてはいけません。これは大きなメリットです。

一方で、RtRアンプは出力段が段重ねにできないため、必然的にトランジスタ(またはFET)一発となります。これはクロス結合フィードフォワードだろうが、その他のトポロジーでも同じです。これが意味するのは、出力に重い負荷(10Ωとか)をつなぐと、出力段のベースからゲインを稼いでる部分まで影響が及び、最終的にオープンループゲインが大幅に低下します。これは宿命とも言える構造上の問題で、どうあがいても避けることができません。唯一の策はFETの出力段にしてインピーダンスの高いゲートにしてしまうことです。こうすると負荷がかかっても大丈夫です。そのかわり電源電圧はある程度盛る必要があります。

そして巷でちょこちょこ聞いていた、TIっぽい音、これ説明つくんじゃないかなと思います。現在のTIのオーディオオペアンプは、全面的にクロス結合フィードフォワードを使用しています。つまり、重い負荷に弱いんです。ヘッドホンとかイヤホンって小出力ながら低インピーダンスですから必然的にオープンループゲインが低下してるはずです。もしかしたら私の知らない方法で、負荷を分離しているかもですが。

結論から言うに、

Rail to Railオペアンプアンプに重い負荷をつなげるべきではない

ということになりました。これはかなり重要だと思っていて、オペアンプ一発のヘッドホンアンプでRtRアンプを選ぶのはナンセンスだということになります。正直、こういった弱点があることは実際に設計して初めてわかったことです。なので、ヘッドホンアンプ用でRtR出力のアンプを作るのは保留としました。

私なりのオペアンプの設計

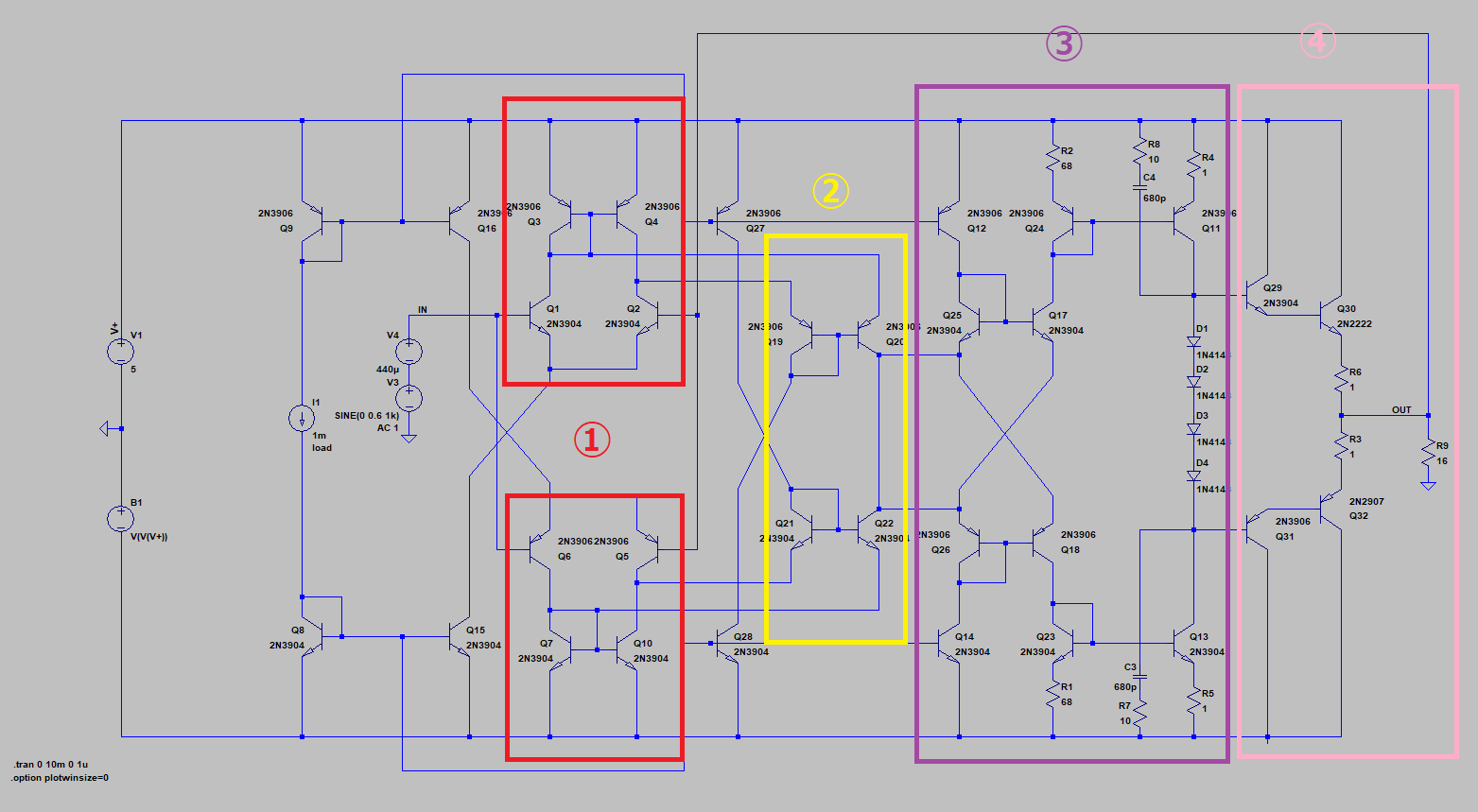

上記の結果から、私なりのオペアンプの設計方法について見えてきました。これらのノウハウをまとめた内容のものを作ってみるとこちらになります。

このオペアンプは4つのブロックに分かれています。

①差動入力段(赤)

最初はよくある差動で動く入力段となります。唯一の特徴は上下でコンプリメンタルとなっていることです。これをすることで、インプットをRtRできます。出力と違ってここではRtRのデメリットが見当たらないのでそのまま採用しました。

②フォールデットの増幅段(黄)

これは巷ではあまり見かけませんが、フォールデット回路の応用でゲインを稼ぐ回路です。入力からそのままつないで行ける上、出力反転しないので便利な回路です。ついでにベース接地の形なので周波数特性も良いです。

③Rail to railのプリドライバ(紫)

え、結局RtR使ってるの?と思われるかもしれませんが、これはあくまでプリドライバ。負荷とは分離されています。あくまで増幅段から出力段までつなぐためだけの回路ですね。

そしてここがかなり特徴的です。増幅段をQ17とQ18がVI変換してしています。ベース接地ですね。クロスした部分により、ベースのバイアスが一体となっていて、常に一緒に動きます。これはつまり歪が原理的に生まれない回路になってます。なおかつミラー回路に渡すことで、RtRのドライバとして機能します。

この部分は結構応用効くと思います。

あと、位相補償が入っていますが、こちらはR=4.7のC=2200pのほうが良さそうです。ここはアプリケーションによって調整ですね。

④出力段(桃)

最後に出力段です。これは先のプリドライバからダーリントン出力になっているだけなので、よく見る回路ですね。特に説明することはないです。強いて言えば、プリドライバと出力を分離するので、重い負荷をかけてもゲインが下がりません。RtRではありませんが、低歪な出力には必須と判断しました。

ボード線図

線図的にはこちらになります。

ちょっとみえずらいですね。裸利得は70dBと控えめです。ただ、この利得は負荷によって変動しません(10Ωから無負荷まで)。これが良いところです。GB積は15MHzくらいです。使ってるトランジスタが2N3904と3906のペアなのですが、これがほぼ限界値と言っていいです。①から③までの設計において、無駄な位相遅れは一切発生していません。1ポール1ゼロの保証での限界値だと思います。

計算上のTHD

100倍のゲインで10Ωの負荷、1Vppの出力のときのTHDがこれです

かなり厳しい条件ですが、歪は-80dB以下です。負荷を下げたり、ゲインを下げれば更に低歪になります。歪の発生しづらい設計と負荷を分離したことで、高い負荷駆動能力と低いTHDが両立しました。

駆け足となりましたが、このようにうまく特徴を取り合わせた回路を作ることで、非常に高性能なオペアンプが設計できました。

次回はこの回路を作ってみたいと思います。