さて、休み中暇なので、次なる試作をしています。ディスクリートのオペアンプの原理試作が終わり、弱点がわかったのでそれをカバーする設計を行いました。主な改良点は、二段増幅を一段増幅に、高速な設計、Rail to rail出力を廃して負荷に強いダーリントン出力に。

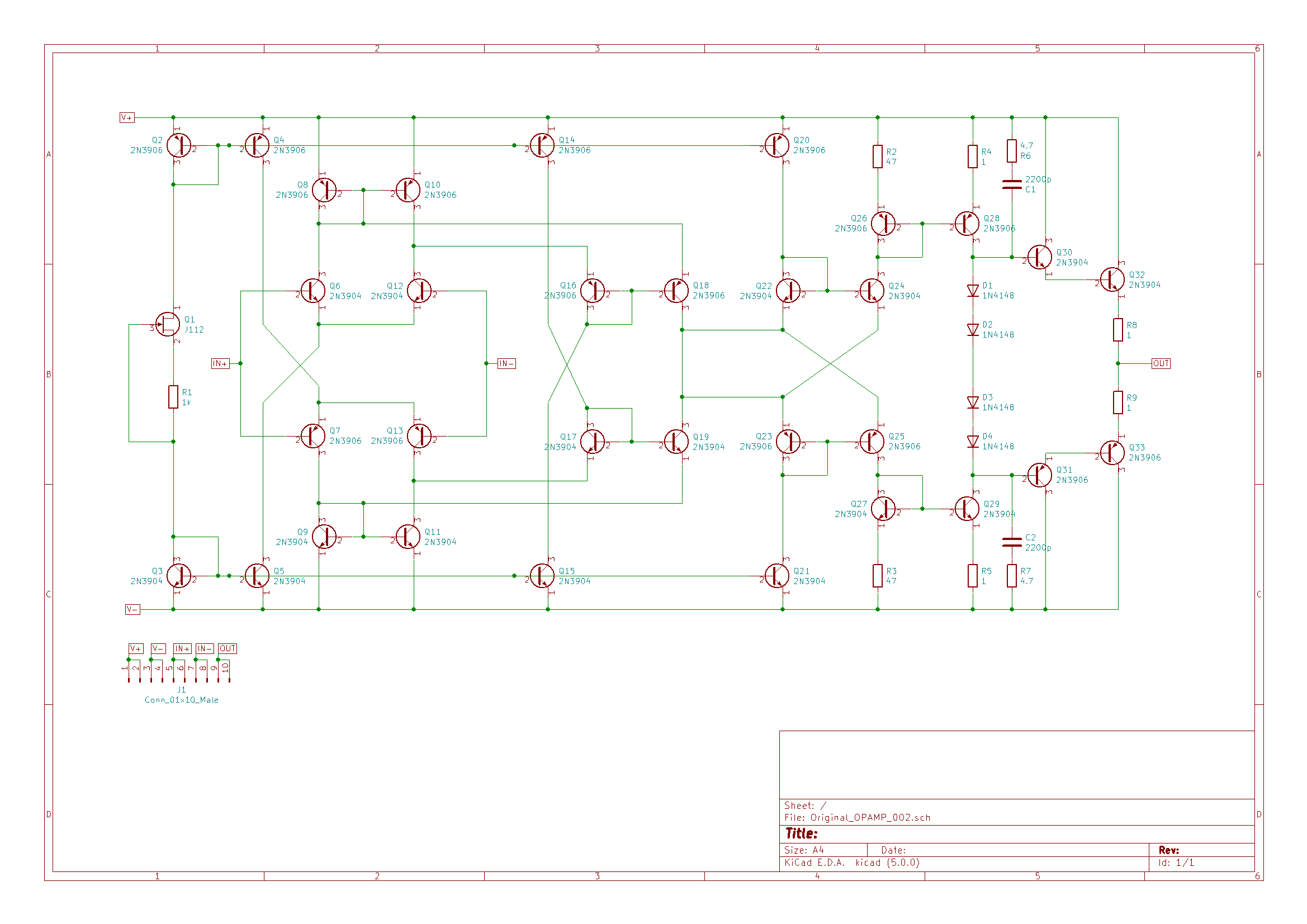

これらをまとめた回路が以下になります。

特徴的な部分がありますので、前回の記事を参考にしてください。

オペアンプについて考察

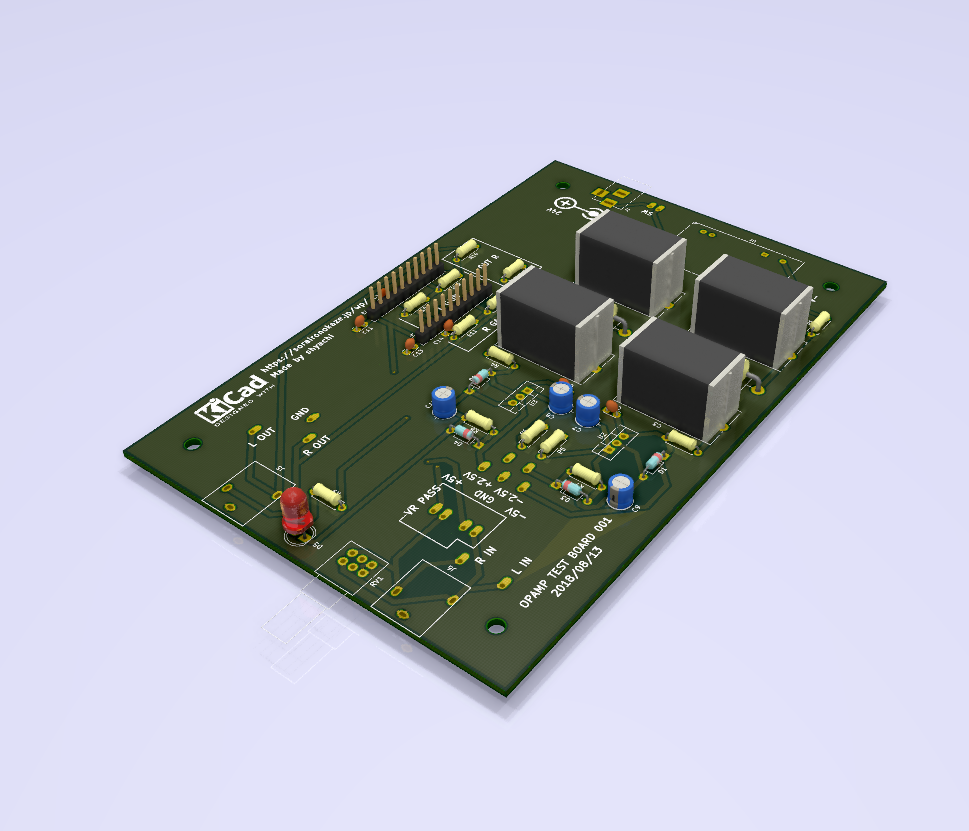

これの実装図はこんな感じ。

やはり金欠のため、部品は秋月縛り。安価な2N3904と2N3906ペアを使っています。この間作ったアンプはSOT-23だったのですが、熱に弱いことわかったので、あえてTO-92としてます。

また、モジュール形式としたことで、ベースの基板と分離しました。本当はDIP-8に乗ればよかったのですが、大きすぎたので、単なるピンヘッダとしました。

ベースとなる回路はこちら。

相変わらず見えづらい図面だ…。説明しますと、24VのDCジャックから絶縁型のDCDC(±5V)を得て、33kHzの二次のLPFを通ります。そしてLM317とLM337のペアで±2.5Vに落として電源としています。

他の装備品はシンプルで、インとアウトのジャック、ボリューム、LEDです。あとは各種テストポイントと調整用のジャンパーを設けています。

実装図はこんなイメージ。

手前の面にインターフェイス、奥にDCジャックとしています。中央の上部にビデオカードのように先程のオペアンプを差し込むようにしています。

こうやって見ると、フィルター段がかなりでかい。フィルムコンデンサ使ってるから仕方ないかな。

現在PCBwayに発注済みで、来週には組み立てに入れそうです。

楽しみだー。